Régulateurs à faible décrochage expliqués

Leur petite taille et leur faible bruit font des régulateurs à faible chute de tension la solution idéale pour les fonctions de point de charge des puces.

Les régulateurs à faible chute de tension (LDO) jouent un rôle très important dans la gestion de l’alimentation d’un circuit intégré. Par conséquent, une conception et une sélection réfléchies des circuits LDO deviennent cruciales. Cet article traite des caractéristiques importantes et des aspects de conception des régulateurs à faible chute et de leur réalisation pratique.

Comme l’exige la tendance des circuits intégrés, les tensions d’alimentation diminuent de jour en jour. De plus, les systèmes avancés sur puces (SoC) utilisent une tension plus faible fournie à mesure que la taille des caractéristiques des processus de fabrication CMOS diminue de manière constante. Par conséquent, pour répondre au besoin d’appareils électroniques modernes fonctionnant sur batterie, la demande augmente pour des alimentations à faible bruit hautement régulées pour circuits intégrés.

Les régulateurs à faible chute de tension (LDO) sont l’un des candidats idéaux pour les régulateurs de tension DC-DC à faible bruit. Ils sont de petite taille, génèrent un faible bruit et sont idéaux pour être utilisés comme régulateurs de point de charge (POL) placés près du circuit cible sur la puce.

Ces régulateurs sont plus simples et plus faciles à mettre en œuvre que les convertisseurs à découpage. Les avantages des LDO par rapport aux régulateurs linéaires conventionnels, outre le faible bruit et la compacité, sont qu’ils ont une faible tension de chute, une stabilité de tension de sortie élevée et une faible dissipation de puissance.

La tension de décrochage mentionnée précédemment est la différence entre la tension d’entrée et de sortie. Les LDO ont une faible tension de chute et sont donc plus efficaces que les régulateurs linéaires conventionnels. Cependant, les régulateurs linéaires comme les LDO doivent dissiper la puissance et, par conséquent, ils ne sont pas aussi efficaces que les régulateurs à découpage. Mais en raison de la faible tension de chute, la dissipation de puissance dans les LDO est nettement inférieure.

Les LDO sont le plus souvent utilisés dans les appareils alimentés par batterie. Par exemple, si un LDO de 2,8 V est connecté à une batterie de 4,2 V (lorsqu’elle est complètement chargée) et que la tension de décrochage du LDO est d’environ 200 mV, alors le LDO peut maintenir la tension de sortie de 2,8 V idéalement même lorsque la tension de la batterie chute à 3V. Dans certains cas, les LDO sont utilisés pour la post-régulation ou le filtrage. Ils peuvent être connectés en sortie d’un régulateur à haut rendement pour assurer le filtrage du bruit.

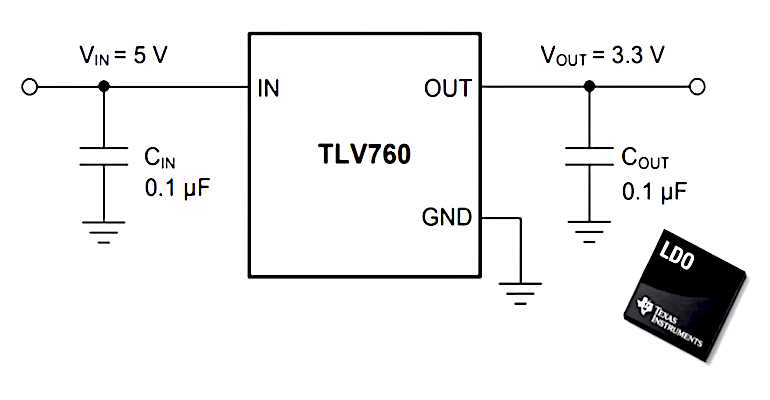

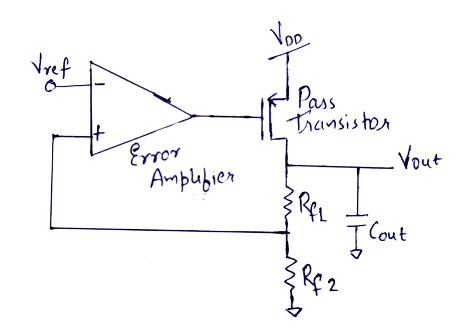

Le fonctionnement d’un régulateur LDO est assez simple. Généralement, les LDO conventionnels se composent d’une référence de tension, d’un amplificateur d’erreur, d’un réseau de détection de tension principalement mis en œuvre par un diviseur de tension et d’un transistor de passage PMOS.

Le transistor de passage est contrôlé par l’amplificateur d’erreur, qui compare la tension de référence et la tension de rétroaction de la sortie, et amplifie la différence. Si la tension de rétroaction est supérieure à la tension de référence, la porte PMOS est tirée vers le haut, permettant à moins de courant de passer et, à son tour, diminuant la tension de sortie.

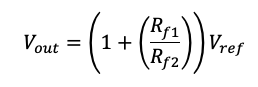

Pour le circuit donné, la tension de sortie est donnée par :

Pour mieux comprendre comment concevoir ou sélectionner chaque étape d’un régulateur LDO, il est nécessaire d’examiner certaines spécifications ou caractéristiques importantes de LDO et de savoir comment certaines étapes d’une conception LDO les affectent.

Sommaire

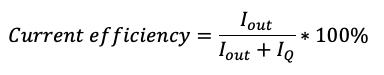

Courant de repos

Courant de repos (jeQ) fait référence au courant consommé par le LDO lorsqu’il est actif. C’est le courant qui traverse la borne de terre. Par conséquent, il est également connu sous le nom de courant de terre ou jeterre. Le courant de repos est un paramètre très important d’un LDO car les circuits CMOS fonctionnent principalement sous une faible charge.

Pour comprendre à quel point jeQ affecte l’efficacité d’un LDO, considérons une batterie de 2,3 V alimentant un circuit de 1,8 V de 2 µA de consommation de courant via un LDO de courant de repos de 1 µA. Cela signifie que même s’il n’y a pas de charge attachée au LDO, 1µA de courant circulera à travers les circuits internes et une certaine puissance sera dissipée.

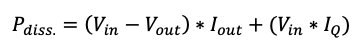

Le calcul de la puissance totale dissipée par un LDO est simple. Il est donné comme suit :

En branchant les valeurs, nous pouvons voir que jeQ représente environ 69 % de la puissance dissipée totale. Ainsi, pour de faibles charges, jeQ devient un paramètre de conception crucial. le jeQ dépend de l’amplificateur d’erreur et du réseau de rétroaction. Pour baisser le jeQ, la consommation de courant de l’amplificateur d’erreur doit être réduite. De plus, nous devons créer un chemin de rétroaction hautement résistif pour garantir que moins de courant circule dans la borne de terre.

En plus de cela, nous pouvons également observer que plus la tension de décrochage (Vout-Vin) est faible, plus la dissipation de puissance sera faible. Mais lorsque la tension de décrochage est trop faible, elle entraîne les circuits internes en saturation, ce qui se traduira par une augmentation du courant de repos.

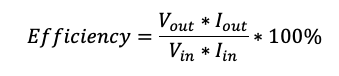

La demande d’abaissement du courant de repos peut également être vue par l’équation d’efficacité :

Où jeDANS = jeEN DEHORS + jeQ

Dans la plupart des cas, la sortie et la tension d’entrée sont prédéterminées. Par conséquent, l’équation d’efficacité se réduit à l’efficacité actuelle.

Ainsi, pour atteindre une efficacité maximale, jeQ doit être minimale. Mais il y a un compromis. La diminution du courant de repos réduira également la vitesse du LDO. Les nœuds internes d’un LDO nécessitent une bonne quantité de courant pour charger les capacités parasites lorsqu’un transitoire se produit.

Abaisser le jeQ entraînera une charge lente de ces condensateurs et, par conséquent, un temps de réponse plus lent. Plus d’informations sur la vitesse d’un LDO sont couvertes dans les caractéristiques de réponse transitoire.

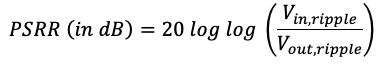

PSRR (rapport de rejet d’alimentation)

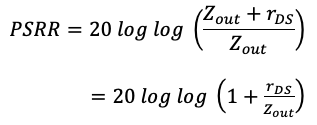

Dans de nombreux cas, les LDO sont utilisés pour rejeter les ondulations de tension d’alimentation. Ces applications exigent que la capacité d’un LDO à supprimer les ondulations de tension soit élevée. PSRR est la capacité d’un LDO à supprimer les ondulations de tension d’entrée. Il s’exprime comme suit :

Le PSRR d’un LDO doit idéalement être très élevé pour toutes les fréquences. Pour optimiser un LDO pour un PSRR élevé, il est nécessaire de comprendre quels facteurs déterminent le PSRR.

Dans la figure ci-dessus, nous pouvons voir que la tension de grille du PMOS varie lorsque la tension d’entrée varie. Cette variation est due au fait que le PMOS essaie de maintenir une différence de tension constante. Par conséquent, l’ondulation de la tension d’alimentation est atténuée en fonction du rapport entre l’impédance de sortie du LDO et la résistance de sortie du PMOS.

Nous pouvons observer à partir de l’expression ci-dessus que l’impédance de sortie doit être réduite pour obtenir un PSRR élevé. Et on peut également montrer que la rétroaction négative dans le régulateur fait ce travail de réduction efficace de l’impédance de sortie.

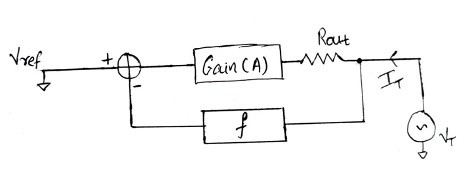

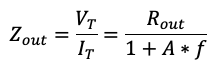

Considérez la boucle de rétroaction comme indiqué dans la figure ci-dessus. L’impédance de sortie peut être obtenue en calculant VJ/jeJ .

.

Le gain de l’amplificateur d’erreur étant très important, de l’ordre de 100 dB, l’impédance de sortie est généralement faible pour les basses fréquences. Mais pour les hautes fréquences, le gain diminue, à son tour, abaissant le PSRR.

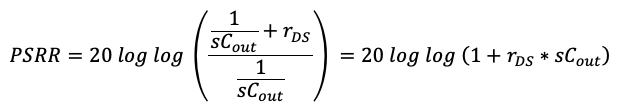

Il existe différentes méthodes pour améliorer le PSRR aux hautes fréquences. Un moyen simple consiste à augmenter la capacité de sortie. Pour voir l’effet d’une capacité de sortie élevée sur le PSRR, nous insérons la valeur de l’impédance de sortie en 1/sCout dans l’équation précédente.

Par conséquent, nous pouvons visualiser qu’un grand condensateur de sortie maintient un PSRR élevé même à des fréquences élevées. Mais un grand condensateur peut également ralentir le temps de réponse d’un LDO. Par conséquent, pour éviter d’utiliser un gros condensateur, on peut utiliser un filtre RC en sortie. Mais cette méthode augmente la tension de décrochage du LDO à cause de la résistance série.

Il existe des méthodes plus sophistiquées pour améliorer le PSRR d’un LDO, comme l’ajout d’un circuit de pompe de charge. Mais la complexité et la dissipation de puissance de tels LDO sont très élevées.

Régulation de charge et régulation de ligne

La régulation de charge est la capacité d’un LDO à maintenir une tension de sortie stable dans des conditions de charge variables.

Généralement, les variations les plus défavorables sont calculées lorsque le courant de sortie passe de 0 au maximum.

La régulation de ligne, d’autre part, est la capacité d’un LDO à maintenir une tension de sortie stable sous une tension d’entrée variable.

Il est trivial de comprendre que pour améliorer la régulation de ligne, le gain en boucle ouverte de l’amplificateur d’erreur doit être très élevé.

Réponse transitoire

Pendant le fonctionnement, si la charge d’un LDO change instantanément, son courant de fonctionnement change rapidement, ce qui provoque une variation progressive du courant de charge du LDO. Idéalement, la tension du LDO doit rester constante dans toutes les conditions. Cependant, il y a un certain retard dû à la vitesse de fonctionnement limitée du LDO. Lorsque la charge change, la rétroaction négative commence à remarquer le changement de charge. Mais entre-temps, la tension drain-source aux bornes du transistor de passage PMOS change instantanément, provoquant une augmentation soudaine de la tension de sortie.

La tension à la sortie pendant les transitoires dépend de l’impédance de sortie et du changement de courant de sortie. La rétroaction ne peut pas suivre immédiatement le changement de courant et réduire l’impédance de sortie. L’ajout d’un grand condensateur de sortie réduira considérablement l’impédance de sortie, améliorant ainsi la réponse transitoire.

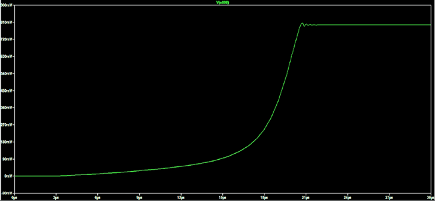

Mais comme nous le savons, un gros condensateur réduit la vitesse d’un LDO. Il existe une autre spécification étroitement liée à la vitesse, à savoir le temps de configuration. C’est le temps nécessaire à un LDO pour s’établir à une tension de sortie. Le temps de configuration est considérablement affecté à mesure que les condensateurs internes augmentent.

Variation de la tension de sortie d’un LDO lorsque le courant de charge varie de 0 mA à 220 mA.

Configurer la forme d’onde transitoire d’un LDO.

Par conséquent, en raison de ce compromis entre vitesse et performances, les concepteurs ont tendance à implémenter un amplificateur d’erreur à vitesse de balayage élevée pour améliorer le temps de configuration.

Comme nous pouvons le voir, il existe de nombreux aspects de conception pour la mise en œuvre d’un régulateur CMOS LDO. De plus, outre une sélection rigoureuse de jeQ, la tension de décrochage, l’impédance de sortie et la conception de l’amplificateur d’erreur, il existe divers autres aspects concernant la stabilité. Les LDO instables ou légèrement stables peuvent connaître des oscillations et, par conséquent, la compensation de la réponse en fréquence des LDO est très critique.

En conclusion, les LDO sont au cœur des circuits de gestion de l’alimentation CMOS, et leur conception est très cruciale si l’on veut obtenir une faible consommation d’énergie et une alimentation fiable.