Pourquoi la gigue d’horloge est-elle un gros problème alors que PCIe 5 Gen s’installe dans le centre de données moderne ?

Les communications par bus série haute vitesse Gen5 PCIe deviennent un élément essentiel du centre de données hautes performances.

La norme PCIe, ou Peripheral Component Interconnect Express, existe depuis près de 20 ans. Il s’agissait d’une mise à niveau du précédent bus PCI, développé par Intel et introduit en 1992. Le bus fournissait une interface parallèle 32 bits, bien que la norme autorisait les architectures 64 bits.

Aujourd’hui, le PCIe est un bus de communication série à haut débit, qui ressemble davantage à un réseau sur carte qu’à l’ancienne interface parallèle PCI. En tant que bus série moderne, la norme PCIe peut implémenter SerDes, qui fait référence à la sérialisation et à la désérialisation des données numériques utilisées dans la communication puce à puce haute vitesse. Les SoC modernes pour le calcul haute performance (HPC), l’intelligence artificielle (IA), l’automobile, les applications mobiles et Internet des objets (IoT) implémentent SerDes via PCI Express (PCIe), MIPI, Ethernet, USB et d’autres normes.

L’une des dernières applications pour PCIe se trouve dans le centre de données. Alors que la demande d’applications à ultra-faible latence et d’IA et d’apprentissage automatique (ML) augmente, les centres de données sont contraints d’ajouter des serveurs pour répondre aux pics de demande. Cependant, les serveurs ont généralement la même taille en termes de ratios de capacité de calcul, de mémoire et de réseau. Mais étonnamment, la charge de travail moyenne à forte intensité de calcul n’utilise pas toujours toute la mémoire disponible. Une telle utilisation inefficace des ressources mémoire est la raison pour laquelle certains centres de données optent pour une utilisation accrue des serveurs virtuels.

L’utilisation de PCIe dans la salle de données a suscité beaucoup plus d’intérêt grâce à l’adoption du nouveau Compute Express Link ou CXL, une interconnexion standard ouverte pour les applications haut débit processeur-périphérique et processeur-mémoire. CXL s’appuie sur la technologie PCI Express (PCIe) en adoptant le PCIe 5.0 PHY comme interface physique. Avec les plates-formes de serveurs de nouvelle génération offrant la prise en charge de la génération PCIe 5.0, un écosystème croissant de périphériques PCIe 5.0 sera proposé sur le marché.

Composants PCIe

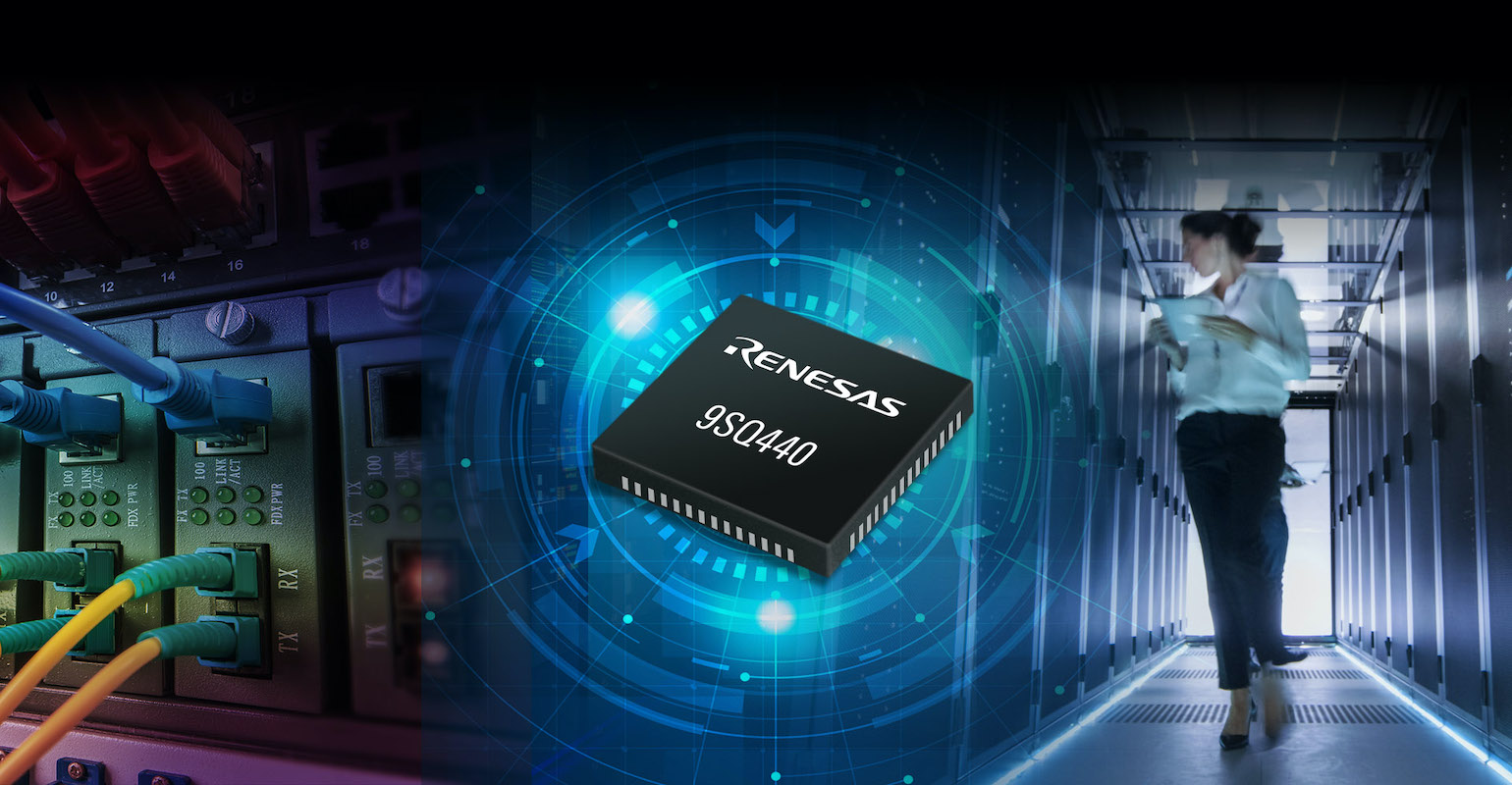

De nombreux fournisseurs de composants proposent désormais des périphériques améliorés pour permettre la migration continue de PCIe dans la salle de données. Pour réussir, ces composants doivent prendre en charge les processeurs basés sur serveur, c’est-à-dire répondre aux Spécification Intel CK440Q et futures exigences du processeur Intel Xeon.

Un composant important dans toute conception PCIe est le générateur d’horloge. Récemment, Renesas a présenté un nouveau circuit intégré générateur d’horloge à faible gigue conçu spécifiquement pour la prochaine génération de centres de calcul et de données hautes performances. Le périphérique 9SQ440 de la société est un générateur d’horloge compatible avec le serveur Intel CK4440Q qui répond aux défis de conception PCIe Gen5.

Les générateurs d’horloge PCIe sont au cœur de la synchronisation PCIe et avec des exigences de spécifications plus strictes pour la dernière norme. Les meilleurs générateurs d’horloge compatibles PCIe Gen5 offrent une flexibilité de conception et une marge significatives aux clients. Ces périphériques peuvent servir de générateur d’horloge centralisé pour les horloges CPU et PCIe du serveur. Les circuits intégrés prennent également en charge les sorties différentielles ainsi que les performances de gigue – moins de 50 fs RMS de gigue de phase d’horloge commune PCIe Gen5 – pour répondre aux exigences de synchronisation des topologies allant des systèmes simples à 2 sockets à carte unique aux systèmes multi-sockets complexes et modulaires.

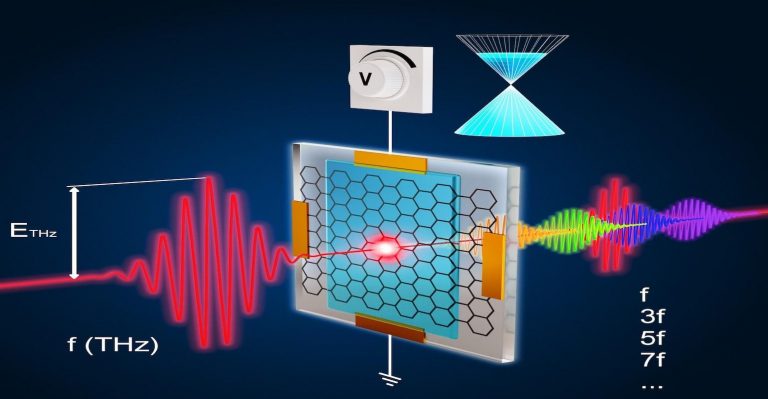

Quelle que soit la génération du bus PCIe, l’horloge reste le composant matériel le plus basique. Le générateur d’horloge produit le signal de synchronisation qui contrôle le débit de données du bus. Traditionnellement, un tampon d’horloge est utilisé pour contrôler le temps de montée et de descente des fronts d’horloge. Le maintien du temps de montée et de descente de l’horloge le plus propre est rendu difficile par la présence de gigue, qui provoque la dégradation du bord de l’horloge par rapport à son emplacement et sa forme idéaux. La gigue d’horloge est généralement causée par les circuits du générateur, le bruit thermique, les variations de l’alimentation électrique et les interférences couplées à des circuits voisins.

À mesure que les vitesses de données augmentent avec chaque génération de bus PCIe, le potentiel de gigue augmente également. Pourtant, la spécification de gigue réelle pour l’horloge est constamment abaissée pour répondre aux problèmes de vitesse et de synchronisation. Pour référence, la limite de gigue PCIe Gen4 est de 500 femtosecondes (fs) rms, alors que la limite Gen3 était de 1 picosecondes (ps) rms. Le budget de gigue pour l’horloge de référence dans un système PCIe Gen5 est de 250 fs max.

Ainsi, le générateur d’horloge est l’élément le plus crucial pour maintenir les performances et la fiabilité appropriées du système PCIe.

Générateur d’horloge compatible avec les serveurs de salle de données pour PCIe Gen5 et au-delà.