Comment conçoit-on vraiment pour le test ? Les experts ETC partagent leurs secrets

Les récents intervenants à la European Test Conference (ETC) ont tout dit sur les tests.

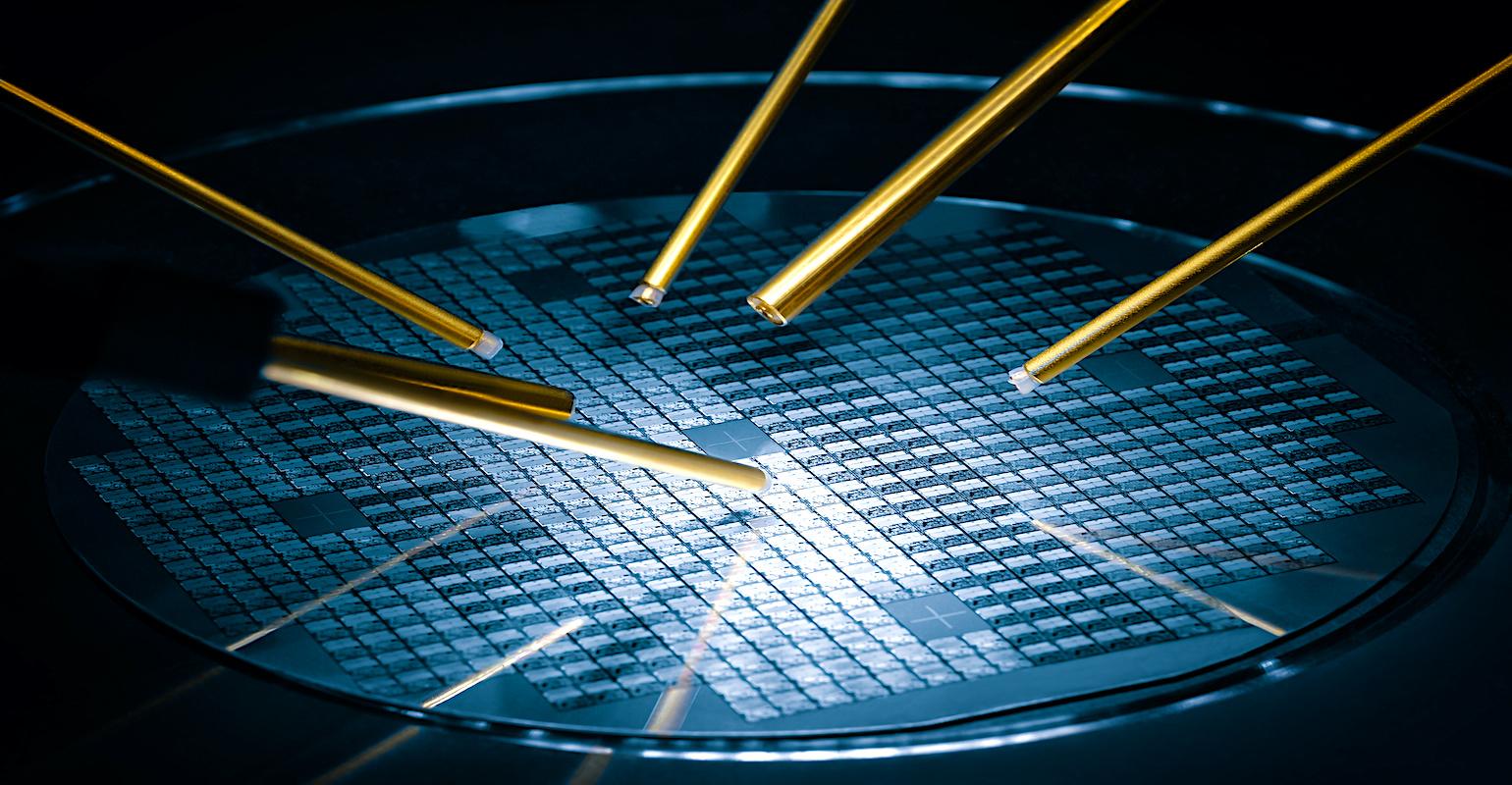

Le test et la vérification des puces semi-conductrices était un sujet important lors de la conférence European Test Systems (ETS) de cette année, en particulier dans le domaine des outils et techniques de conception pour test (DFT). Cadence, Siemens et Synopsis ont discuté des différents aspects des défis de test en cours.

Par exemple, la précision, la résolution et les performances d’un outil de diagnostic de panne basé sur l’analyse sont extrêmement critiques pour permettre un test plus rapide des puces de silicium et améliorer les rendements globaux. Les méthodes de diagnostic par balayage sont utilisées pour identifier et localiser les défauts des semi-conducteurs sur les appareils qui échouent au test de fabrication ou qui sont renvoyés du terrain. Mais sélectionner les appareils de test appropriés pour l’analyse des défaillances est un défi. Pour résoudre ce problème, certains fabricants de semi-conducteurs ont intégré le diagnostic par balayage dans le processus d’analyse de rendement.

La plupart des défis de diagnostic sont exacerbés par des tailles de conception sans cesse croissantes, des architectures de conception pour test (DfT) complexes et de nouveaux types de défauts, a noté Sameer Chillarige de Cadence Design Systems dans sa présentation virtuelle ETC. Ces défis rendent le processus global beaucoup plus fastidieux et gourmand en ressources. Chillarige s’est concentré sur les capacités de diagnostic de haut niveau de la solution logicielle Modus DfT pour fournir des moyens d’offrir une précision, une résolution et des performances élevées pendant le processus de diagnostic.

Alors que les géométries des puces ont continué à se rétrécir – même avec le ralentissement des avantages de la loi de Moore – les difficultés pour tester et vérifier les conceptions de la puce ont augmenté. Geir Eide de Siemens s’est penché sur la façon dont la complexité croissante des conceptions de grands systèmes sur puce (SoC) présente des défis spécifiques à l’approche DfT, en particulier pour les méthodes DfT hiérarchiques traditionnelles. Eide a expliqué comment la technologie Tessent Streaming Scan Network (SSN) aide à réduire les compromis entre l’effort de mise en œuvre des tests et le coût des tests de fabrication en découplant le DfT au niveau du cœur et au niveau de la puce.

Conception-pour-test

Design-for-Test (DfT) est une méthodologie de développement de puces semi-conductrices qui ajoute des fonctionnalités de testabilité à une conception de produit matériel. Une approche DfT et les outils associés visent à s’assurer que le matériel du produit ne contient aucun défaut de fabrication qui pourrait affecter son fonctionnement.

Les techniques DFT ont été utilisées au moins depuis les premiers jours des équipements de traitement électronique des données. Les premiers exemples des années 1940/50 utilisaient des commutateurs et des instruments pour « balayer » (c’est-à-dire, sonder sélectivement) la tension et le courant à des nœuds internes spécifiques dans un ordinateur analogique.

Le cycle de développement de produits pour les circuits intégrés complexes d’aujourd’hui est en constante diminution. Ce n’est pas une nouvelle tendance. Le défi est de s’assurer que le coût accru pour tester un transistor (ou un registre) n’est pas supérieur au coût de fabrication. Une façon de remédier à ce déséquilibre des coûts est de s’assurer que le test est considéré comme une exigence de conception, en particulier un test de fabrication. C’est l’idée de base derrière l’approche populaire de conception pour test (DFT) pour le développement de circuits intégrés.

Une façon d’effectuer de tels tests consiste à intégrer des chaînes de balayage dans du silicium. Mais de telles chaînes de balayage nécessitent un équipement de test automatique (ATE) pour effectuer les tests avec les chaînes. Il n’est donc pas surprenant que les fournisseurs d’outils de test EDA aient travaillé en étroite collaboration avec les fournisseurs ATE pour gérer efficacement les modèles de test basés sur l’analyse et pour minimiser le temps d’application des tests pour les modèles d’analyse. De cette façon, les approches DfT réduisent le coût des tests en réduisant le nombre total de motifs de test nécessaires pour vérifier la « conformité » d’une puce.

Le logiciel générateur de programme de test automatique (ATPG) génère des vecteurs de test pour l’ATE. Ainsi, les augmentations de la complexité des puces correspondent directement à des augmentations du nombre de motifs de test requis pour assurer un niveau de test équivalent.

Test des modules multi-puces

La dernière présentation à l’ETC de cette année s’est concentrée sur le processus réel de test des modules multi-puces (MCM). Un MCM est un moyen courant de combiner plusieurs puces de circuits intégrés (CI), des puces semi-conductrices et d’autres composants discrets sur un substrat unificateur. Ainsi, l’ensemble du module peut être traité comme un circuit intégré plus grand. L’utilisation de l’emballage MCM permet à un fabricant d’utiliser plusieurs composants pour la modularité et/ou d’améliorer les rendements par rapport à une approche IC monolithique conventionnelle.

Mais les avantages d’un MCM peuvent être dépassés si l’emballage tombe en panne tard dans le processus de fabrication lors des tests intégrés finaux. Comme Guy Cortez de Synopsys l’a souligné dans sa présentation, de tels échecs entraînent la possibilité de vendre ces puces et rendent impossible la récupération des coûts élevés associés aux tests et à l’emballage nécessaires à la fabrication de ces puces MCM défaillantes.

Cependant, l’utilisation de l’analyse de données tout au long des différentes étapes de test de fabrication peut aider à trouver la source du problème plus tôt dans le cycle de fabrication. Cortex a introduit des méthodes d’analyse spécifiques telles que la remontée des données et la remontée des données qui ont permis aux ingénieurs de test d’effectuer une analyse rapide des causes premières et de trouver la source du problème. Les ingénieurs de test pourraient ensuite incorporer des mesures préventives pour éliminer les puces suspectées plus tôt dans le processus, évitant ainsi des défaillances coûteuses en aval.

Alors que les puces continuent de croître en complexité de conception, les activités de test et de fabrication augmentent également. Heureusement, le monde des outils EDA est au-dessus de l’ensemble du processus de développement des puces.